Practical PCB layout design rules for creating high performance circuit boards

1. PCB Layout

Ten rules for component layout:

Follow the principle of "from large to small, from difficult to easy" in the layout, meaning that important circuit units and core components should be prioritized.

The layout should reference the schematic diagram and arrange the main components according to the primary signal flow direction of the board.

Components should be arranged to facilitate debugging and maintenance. That is, large components should not be placed near small ones, and there should be enough space around components that require adjustments.

For circuits with similar structures, use a "symmetrical" standard layout whenever possible.

Optimize the layout based on standards of uniform distribution, balanced center of gravity, and aesthetic appearance.

Components of the same type should be placed in the same direction along the X or Y axis. Polarized discrete components of the same type should also be aligned consistently in the X or Y direction to facilitate production and inspection.

Heat-generating components should be evenly distributed to facilitate heat dissipation for both the board and the entire device. Temperature-sensitive components, except for temperature detection elements, should be placed away from components that generate significant heat.

The layout should ideally meet the following requirements: overall wiring as short as possible, critical signal lines the shortest; high voltage and large current signals should be completely separated from small current and low voltage signals; analog and digital signals should be separated; high-frequency and low-frequency signals should be separated; and sufficient spacing should be maintained between high-frequency components.

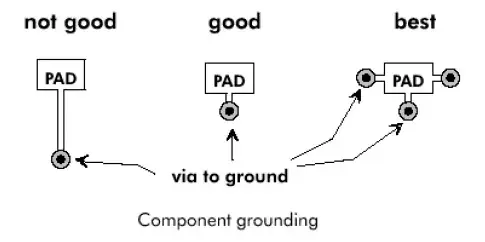

The layout of decoupling capacitors should be as close as possible to the power pins of the IC, minimizing the loop formed between the power and ground.

When laying out components, consider placing devices using the same power supply together to facilitate future power partitioning.

2. Wiring

1. Wiring Priority

(1) Critical signals should be prioritized.

Prioritize wiring for critical signals such as analog small signals, high-speed signals, clock signals, and synchronization signals.

(2) Density Priority Principle

Start wiring from the most complex connections on the board. Begin with the densest areas of the board.

(3) Points to Note

Try to provide dedicated routing layers for critical signals such as clock signals, high-frequency signals, and sensitive signals, ensuring the minimum loop area. When necessary, prioritize manual routing, shielding, and increasing safety distances to ensure signal quality.

- The EMC environment between the power and ground layers is usually poor, so it’s advisable to avoid placing interference-sensitive signals here.

2. Four Specific Routing Methods

(1) Clock Routing

The clock line is one of the most significant factors affecting EMC. Minimize vias on the clock line, avoid parallel routing with other signal lines, and keep it away from general signal lines to prevent interference. Also, avoid routing near the power section of the board to prevent mutual interference between power and clock. If there is a dedicated clock generation chip on the board, no routing should be done underneath it; instead, copper should be laid under it, and ground separation should be applied if necessary. For many chips with a reference crystal oscillator, no routing should be done under these crystals, and copper should be laid to isolate them.

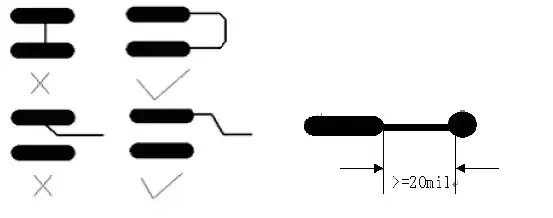

(2) Right-Angle Traces

Right-angle traces are generally something to avoid in PCB routing, and they have almost become a standard for judging the quality of routing. But how much do right-angle traces really impact signal transmission? Theoretically, right-angle traces cause the width of the transmission line to change, leading to impedance discontinuities. In fact, it's not just right-angle traces—acute and obtuse angle traces can also cause impedance variations.

The impact of right-angle traces on signals mainly manifests in the following aspects:

The corner can be equivalent to a capacitive load on the transmission line, which slows down the rise time.

Impedance discontinuities can cause signal reflections.

The sharp tip of a right-angle trace can generate EMI (Electromagnetic Interference).

(3) Differential Traces

Differential signals are increasingly being used in high-speed circuit design. The most critical signals in a circuit often use a differential structure. To define it simply, the driver sends two equal but opposite signals, and the receiver determines the logical state, "0" or "1," by comparing the difference in voltage between the two signals. The pair of traces carrying the differential signals are referred to as differential traces.

Compared to ordinary single-ended signal traces, differential signals have the following significant advantages:

Strong anti-interference ability: The coupling between the two differential traces is very good, so when external noise interference occurs, it is almost simultaneously coupled to both traces. Since the receiver only cares about the difference between the two signals, any common-mode noise from the external environment can be completely canceled out.

Effective suppression of EMI: For the same reason, because the signals are of opposite polarity, the electromagnetic fields they radiate can cancel each other out. The tighter the coupling, the less electromagnetic energy is emitted to the outside.

Accurate timing positioning: The switching of differential signals occurs at the crossing point of the two signals, unlike ordinary single-ended signals, which rely on high and low threshold voltages. This reduces the impact of variations in manufacturing and temperature, minimizing timing errors. This makes differential signaling especially suitable for low-amplitude signal circuits. The popular LVDS (Low Voltage Differential Signaling) technology refers to this type of small amplitude differential signaling.

For PCB engineers, the primary concern is how to ensure that these advantages of differential traces are fully realized in practice. Anyone familiar with layout design is likely aware of the general requirements for differential traces, namely "equal length and equal spacing."

Equal length ensures that the two differential signals maintain opposite polarities at all times, reducing common-mode components; equal spacing ensures that the differential impedance remains consistent, minimizing reflections. The "as close as possible" principle is also sometimes a requirement for differential traces.

(4) Serpentine Traces

Serpentine traces are a commonly used routing method in layout design. Their main purpose is to adjust delay and meet the system's timing design requirements.

Designers should first recognize the following:

Serpentine traces can degrade signal quality and alter transmission delay, so they should be avoided whenever possible. However, in actual design, to ensure that signals have sufficient hold time or to reduce timing skew within a group of signals, intentional serpentine routing is often necessary.

Points to Note:

Paired differential signal lines should generally be routed parallel to each other, with as few vias as possible. When vias are necessary, both lines should have matching vias to achieve impedance matching.

A group of bus lines with the same attributes should be routed in parallel and as equal in length as possible. Vias drawn from SMT pads should be placed as far from the pads as possible.

3. Common Routing Rules

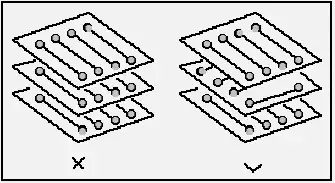

(1) Rules for Controlling Routing Direction

The routing direction of adjacent layers should form an orthogonal structure. Avoid routing different signal lines in the same direction on adjacent layers to reduce unnecessary crosstalk between layers.

If this is difficult to avoid due to board structure limitations (such as in certain backplanes) and the signal speed is high, consider using ground planes to isolate the routing layers, and then use ground signal lines to isolate the signal lines.

(2) Open Loop Check Rule for Routing

In general, routing with one end left floating (Dangling Line) is not allowed. This is mainly to avoid creating an "antenna effect," which can reduce unnecessary interference, radiation, and reception. Otherwise, it may lead to some unpredictable results.

(3) Impedance Matching Check Rule

The width of traces within the same network should remain consistent. Variations in trace width can lead to uneven characteristic impedance, which may cause reflections at higher transmission speeds. This situation should be avoided in the design.

In certain conditions, such as with connector leads or BGA package leads, where it may be unavoidable to have variations in trace width, efforts should be made to minimize the length of the inconsistent portions.

(4) Trace Length Control Rule

Short Trace Rule: In design, traces should be kept as short as possible to minimize interference issues caused by excessive trace lengths. This is particularly important for critical signal lines, such as clock lines, where the oscillator should be placed as close to the relevant component as possible. When driving multiple components, the appropriate network topology should be chosen based on the specific situation.

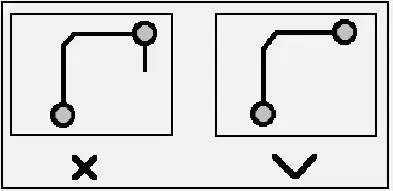

(5) Chamfering Rule

Sharp angles and right angles should be avoided in PCB design as they can cause unnecessary radiation and degrade process performance.

(6) Decoupling Rule for Components

Add necessary decoupling capacitors on the PCB to filter out interference signals from the power supply, ensuring stable power signals.

In multilayer boards, the placement of decoupling capacitors is generally less critical, but in double-sided boards, the layout of decoupling capacitors and the routing of the power supply can directly affect the overall system's stability, sometimes determining the success of the design.

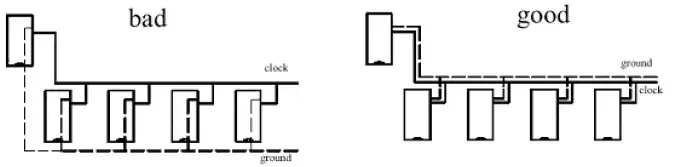

In double-sided board design, the current should typically pass through the filter capacitor before reaching the components.

In high-speed circuit design, the correct use of decoupling capacitors is crucial for the stability of the entire board.

(7) Component Layout Partitioning/Layering Rule

This rule primarily aims to prevent mutual interference between modules operating at different frequencies while also minimizing the trace lengths in the high-frequency sections.

In mixed-signal circuits, the analog and digital circuits can be arranged on different sides of the PCB, with different layers used for routing, and separated by a ground plane.

(8) Ground Loop Rule

Minimize Loop Area Rule: The loop area formed by the signal line and its return path should be as small as possible. The smaller the loop area, the less radiation emitted and the less external interference it receives.

(9) Integrity Rule for Power and Ground Layers

In areas with dense vias, avoid connecting them in the carved-out sections of the power and ground layers, which could fragment the plane layers. This fragmentation can compromise the integrity of the plane layers, leading to an increased loop area for the signal traces in the ground layer.

To reduce crosstalk between traces, ensure sufficient spacing between them. When the distance between the centers of the traces is at least three times the trace width, 70% of the electric field will not interfere with adjacent traces, which is known as the 3W rule. To achieve 98% isolation, a spacing of 10W can be used.

(11) Shielding

Corresponding to the ground loop rule, the goal is to minimize the loop area of signals, which is especially important for critical signals like clock and synchronization signals.

For particularly important and high-frequency signals, consider using a coaxial cable shielding structure. This involves isolating the trace with ground lines on all sides and ensuring effective integration of the shielding ground with the actual ground plane.

(12) Termination Network Rule

In high-speed digital circuits, when the delay time of PCB traces exceeds one-fourth of the signal rise time (or fall time), the trace can be considered a transmission line. To ensure proper impedance matching between the signal’s input/output and the transmission line, various matching methods can be employed. The choice of matching method depends on the network's connection type and the routing topology.

For point-to-point (one output to one input) connections, series termination at the source or parallel termination at the destination can be used. The former has a simple structure and low cost but introduces greater delay. The latter provides better matching but is more complex and costly.

For point-to-multipoint (one output to multiple inputs) connections, when the network topology is a daisy chain, parallel termination at the destination is recommended.

When the network uses a star topology, refer to the point-to-point structure. Star and daisy chain are two basic topologies, and other structures can be seen as deformations of these basic structures. Flexible measures can be taken to achieve matching.

In practice, cost, power consumption, and performance should all be considered. The goal is not always perfect matching; it is sufficient to limit interference, such as reflections, within an acceptable range.

(13) Closed Loop Check Rule for Routing

Prevent signal traces from forming self-loops across different layers. This issue is common in multilayer board design, where self-loops can cause radiation interference.

(14) Trace Branch Length Control Rule

Try to control the length of branches. The general requirement is that Tdelay <= Trise/20.

(15) Resonance Rule for Traces

This rule mainly applies to high-frequency signal design. The trace length should not be an integer multiple of the signal's wavelength to avoid resonance phenomena.

(16) Isolated Copper Area Control Rule

The presence of isolated copper areas can lead to unpredictable issues. Connecting isolated copper areas to other signals can help improve signal quality, usually by grounding or removing the isolated copper.

In actual manufacturing, PCB manufacturers may add copper foil to unused areas of the board to facilitate processing and to help prevent PCB warping.

(17) Overlapping Power and Ground Plane Rule

Different power planes should be avoided overlapping in space. This is mainly to reduce interference between different power supplies, especially between power supplies with significantly different voltages. The issue of overlapping power planes must be avoided whenever possible; if it cannot be avoided, consider using an intermediate ground plane for isolation.

(18) 20H Rule

Due to the varying electric fields between the power and ground layers, electromagnetic interference may radiate outward from the edge of the board, known as the edge effect.

The solution is to retract the power layer so that the electric field is contained within the ground layer. By retracting 20H (where H is the dielectric thickness between power and ground), 70% of the electric field can be confined within the ground layer's edge; retracting 100H can confine 98% of the electric field.

4. Other Considerations

For single or double-layer boards, power lines should be as wide and short as possible. The width of power and ground lines can be calculated based on a current capacity of 1A per 1mm of trace width. The loop formed by the power and ground lines should be minimized.

To prevent noise coupling from long power lines from entering the load components directly, decouple the power supply before it reaches each component. Additionally, to prevent mutual interference between loads, decouple the power supply for each load independently, ensuring that filtering occurs before the power reaches the load.

Maintain good grounding during routing.

Although mistakes are inevitable when designing electronic products, as long as engineers are careful enough and use PCB layout software, the quality of the design is guaranteed, and it is possible to make a perfect board with zero errors.

Many PCB layout software can help design engineers check for manufacturability issues before production, and can meet the various scenarios required by engineers, minimize the number of iterations of product development, and reduce costs.